# REAL-TIME PROCESSING STAGES OF ELECTROCARDIOGRAM SIGNAL: A REVIEW

## <sup>(b)</sup>Rasha Waleed<sup>\*</sup>, <sup>(b)</sup>Noor Talal Gadawe, <sup>(b)</sup>Sahar Lazim Qaddoori

Electronic Engineering Department, Electronics Engineering College, Ninevah University, Mosul, Iraq

Abstract. Signal analysis is a multidisciplinary field that combines various processes to create robust pipelines for automating data analysis. Within the medical field, its application revolves around physiological signals. Electrocardiogram (ECG) signal provides vital information concerning various cardiac conditions affecting the human heart. ECG analysis is a central pillar of medical research with the goal of detecting and preventing potentially fatal cardiac events. This review article aims to provide a comprehensive analysis of real-time processing techniques for electrocardiogram signals. It discusses the different methods and algorithms used for detecting and analyzing ECG signals in real-time, with a focus on their effectiveness and efficiency. Where, it evaluates the use of various techniques such as ECG signal preprocessing (denoising), ECG fiducial points detecting and ECG signal classification. It also highlights the challenges faced in real-time ECG signal processing, such as High-fidelity signal acquisition and noise reduction, and computational efficiency and resource constraints. Furthermore, the article presents an overview of the existing QRS-peak detection strategies, including methods such as Haar wavelet transform, and modified MaMeMi Filter.

Keywords: Electrocardiogram (ECG), preprocessing, feature extraction, classification, FPGA.

Corresponding author: Rasha, Waleed, Electronic Engineering Department, Electronics Engineering College, Ninevah University, Mosul, Iraq, e-mail: rasha.hamad@uoninevah.edu.iq

Received: 15 January 2024; Revised: 4 March 2024; Accepted: 20 March 2024; Published: 30 April 2024.

## 1 Introduction

Globally, cardiovascular diseases hold the highest position as a cause of death. ECG is a valuable diagnostic tool that records heart electrical activity and stands as a valuable diagnostic tool. However, the current clinical practice involves visually inspecting ECGs, which is a time-consuming task, especially for long-term recordings like 24-hour Holter monitoring that can have around 100,000 heartbeats (Abdulla & Al-Ani, 2020; Roth et al., 2020).

Driven by the need for clarity and understanding, this comprehensive review of real-time ECG processing is structuring as a stage-based model to highlight the significance of each step. The initial stage examines the noise removal techniques employed during ECG signal acquisition. The second stage focuses on identifying crucial fiducial points and pivotal for accurate heart condition classification. Each ECG wave and segment carries vital information for classifying arrhythmia types, enabling disease detection and diagnosis in the final stage.

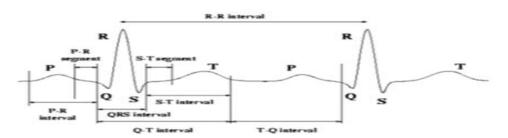

Figure 1 demonstrates the three fundamental components of an ECG, namely the T wave, QRS complex, and P wave, along with their corresponding intervals (M Abdul-Jabbar & Waleed

How to cite (APA): Waleed, R., Gadawe, N.T. & Qaddoori, S.L. (2024). Real-time processing stages of electrocardiogram signal: A review. *Journal of Modern Technology and Engineering*, 9(1), 39-54 https://doi.org/10.62476/jmte9139

Figure 1: ECG Signal showing P-QRS-T Waves

Hamad, 2014). The appearance of the P wave results from electrical potentials when the atria undergo depolarization before contraction begins. Similarly, the QRS complex is produced by potentials generated during ventricular depolarization before contraction, as the depolarization wave spreads through the ventricles. Depolarization of the heart is indicated by both the P wave and the QRS complex. Following the ventricular depolarization, the T wave, known as repolarization, emerges during the recovery phase. This repolarization wave typically occurs within 0.25 to 0.35 seconds after depolarization in the ventricular muscle. Consequently, the ECG comprised depolarization and repolarization waves (Fikri et al., 2021; Guyton, 2006).

This paper focuses on real-time ECG processing, for the detection different arrhythmias and heart conditions. The objectives can be summarized as follows:

- 1. An in-depth analysis of the ECG waveform is essential for gaining a comprehensive understanding of the heart's electrical activity. This review will delve into the various components of the ECG and their significance in reflecting the heart's function.

- 2. Introducing a stages-based model for real-time ECG processing, this paper provides a comprehensive review of related work in ECG real-time processing by covering various stages such as ECG preprocessing and classification.

- 3. This review comprehensively examines real-time ECG signal processing, exploring advanced denoising techniques, accurate fiducial point detection, and robust classification algorithms for arrhythmia diagnosis.

- 4. This paper conducts a comprehensive examination of techniques and methodologies employed at each stage of ECG signal processing, offering valuable insights and illuminating the interconnectedness of relevant research.

- 5. The paper outlines of hardware and software tools for research in the field of ECG signal analysis.

The rest of this paper is structured as follows: Section 2 provides an overview of prior related work in the literature, focusing on various stages of ECG signal analysis, from data preprocessing to classification, which is divided into three subsections: Sub-Section 2.1 tackles noise reduction through smoothing and filtering. Sub-Section 2.2 presents prior related work on ECG fiducial points and other feature detection. Sub-Section 2.3 presents various established models for classifying ECGs, allowing for diagnosis and interpretation. Section 3 dives deep into the hottest research directions in real-time ECG processing, as explored by prominent researchers. In Section 4, a comparative summary is presented. Lastly, Section 5 concludes this article.

## 2 Literature Review of ECG Signal Processing Stages

This article reviews the implementation of ECG processing algorithms published in the last decade. It collects relevant articles from 2016 to 2024 from various resources, including Springer, Elsevier, IEEE, and World Scientific. The review analyzed hardware implementation of ECG preprocessing, feature extraction, and classification stages, comparing different works and providing insights to researchers.

#### 2.1 Stage 1: Preprocessing (Denoising)

ECG processing relies on body-connected sensors. Noise affects signal quality and classification. Preprocessing is crucial for accurate analysis, using digital filters to remove unwanted frequencies and artifacts while preserving relevant components. Researchers have adopted various filters to enhance signal quality, improving interpretation, diagnosis, and patient care in cardiac conditions.

Al-Khammasi et al. (2016) designed FIR filters for ECG denoising, attenuating 60 Hz frequencies using VHDL and Quartus II. Performance analysis favored pipelined MAC implementation with fewer resources, suggesting its use for industrial ECG monitoring to reduce risks.

Gaikwad and Chavan (2016) implemented an ECG noise reduction IIR Chebyshev filter using XSG. The paper emphasized the importance of considering quantization and overflow for filter stability. The filter is analytically designed, simulated in Simulink, and improved speed on FPGA compared to DSPs. It effectively removes noise in ECG signals, and the paper included a comparison of filter types.

Gaikwad and Chavan (2018) proposed an IIR Elliptic digital filter on FPGA for ECG signal noise reduction. The design included MATLAB Simulink and Xilinx System Generator blocks for implementation demonstration. The Vedic multiplier is used for filter implementation. The filter's performance is evaluated in terms of area, power, and speed, highlighting its advantages. The paper presented a detailed step-by-step design process and simulated the results of the filter.

Pathak et al. (2018) introduced an architecture capable of acting as both a notch and antinotch filter. The architecture was implemented as a 2nd order IIR filter on the Xilinx ISE 14.4 program, specifically on the Zynq FPG kit. By applying the retiming concept, the filter's speed was improved by 1.56 times while maintaining accuracy. To reduce hardware complexity in terms of kit area, the notch, and anti-notch filters were combined, resulting in a more efficient solution.

ECG (2018) proposed an architecture for real-time ECG denoising using an adaptive dual threshold filter. The implementation involved structural VHDL description of functional blocks, along with parallelization for accelerated processing and high performance. The architecture is designed for low-cost FPGA-based systems, prioritizing low complexity and resource occupancy. Optimization and simplification were achieved through VHDL implementation.

Venkatesan et al. (2019) introduced a DENLMS adaptive filter to remove white Gaussian noise, improving the quality of ECG signals. The architecture improves operational speed by minimizing critical paths using delay elements. Performance comparisons were made with the ENLMS and DNLMS algorithms. The pipelined DENLMS filter enhances speed and reduces power consumption but increases area due to latches. The evaluation was done using the Virtex 5 FPGA for speed, logic utilization, and power consumption analysis.

Sohal and Jain (2019) proposed a low-power FPGA-based hardware implementation for ECG signal preprocessing. The paper focused on designing FIR filters to remove high- and low-frequency ECG noises. It evaluated various window-based filter designs for their resource utilization and power consumption on the Zynq evaluation board. The preprocessing module is implemented using XSG and targets the Zynq-7000 with the Vivado program. Performance

comparisons revealed Kaiser and Bartlett's window as the most effective in terms of resource utilization and power consumption.

Thirrunavukkarasu et al. (2021) designed an FIR filter using the Kaiser Bessel window for ECG waveform noise removal. The Kaiser filter implemented using the FPGA consists of three Verilog blocks connected by wires. The Kaiser filter, similar to Hamming, incorporates a beta variable to control the filter threshold and is known for its high efficiency and low power consumption.

Mejhoudi et al. (2021) developed an FPGA architecture for ECG signal denoising using a hybrid technique: DWT and ADTF. The hardware-software co-design divided the architecture into functional blocks for parallel processing. This achieved high-performance noise reduction without impacting signal morphology. Simulation results demonstrated the system's effective-ness, processing in 0.3 ms at a 360 Hz acquisition frequency. The architecture efficiently utilized FPGA resources, occupying less than 1% of total registers and logic elements.

Following Patel and Shah (2022), the design was presented for a bandpass filter that can remove many kinds of noises from the ECG signal. The effectiveness of the filter was proved by means of evaluating and performing the power spectrum analysis which means that it is a applicable and real time method for decreasing the noise.

Sohal and Jain (2022) used FPGA-based waveform regeneration algorithms of ECG signals using series window and DWT. The Haar wavelet-based design showed a very good sterling, saving resources and it may be integrated into portable biological devices. There is the capability to compare efficiency between systems and also the systems are evaluated.

A model of reservoir computing at an economical expense by means of FPGA and ECG denoising of high-speed was done by Elbedwehy et al. (2022). An architecture was applied here employing the back propagation recurrence bound with technologically advanced and less complex modules.

Shanmugaraja et al. (2023) designed a pipelined LMS adaptive filter aiming at ECG signal processing, which not only brings the good features of adaptive filters but also is low power consumption. The investigation considered FPGA, which showed the rising speed as compare to other rival methods.

In addition, Vaishnavi et al. (2023) came with a new adaptive filter, which plays efficaciously as an LMS adaptive filter to banish the baseline wander noise from the ECG signals, showing its outstanding result in improving the signals' quality.

Gon and Mukherjee (2023) suggested the efficient reconstruction of FPGA with multiplierless lifting-based wavelet denoising for ECG noise cancellation. Their architecture with the ability to lower resource consumption as well as increase the operating frequency with existing ones and even future ones.

Boumehrez et al. (2023) proposed Lifting 9/7 Wavelet Filter Bank for the analysis of an ECG-signal on the FPGA platform (Cyclone-II). The papers presented alternatives shifting logic instead of the standard left-right (shifting) for multiplication-division operations, which reduces execution time, logic complexity, and power consumption. To be a feasible, we proposed a data structure to facilitate implementing the lifting filter in two-dimensional discrete wavelet transforms.

#### 2.2 Stage 2: Feature Extraction

ECG classification relies on detecting fiducial points, particularly the QRS complex, which reflects ventricular contraction. Its shape enables automated detection of various characteristics, forming the basis for classification techniques. QRS detection is foundational for ECG analysis algorithms. Several approaches have been proposed for feature extraction, targeting the ST-segment, QRS complex, R-peak, and other fiducial points. This section explores the literature on different methods and techniques for hardware implementation of QRS complex, ST-segment, and fiducial point detection.

| (Reference)                         | Method                                                                                        | Database                | Noise                                                                                          | Kit Type                                                      |

|-------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| (Al-Khammasi et al., 2016)          | FIR filter                                                                                    | MIT-BIH arrhyth-<br>mia | 60 Hz Gaussian White<br>Noise                                                                  | N/A*                                                          |

| (K. Gaikwad & Chavan,<br>2016)      | IIR Chebyshev type<br>II                                                                      | MIT-BIH arrhyth-<br>mia | High-Frequency Noise                                                                           | FPGA Spartan 3                                                |

| (K. M. Gaikwad & Chavan,<br>2018)   | IIR Elliptic                                                                                  | N/A*                    | High Frequency Noise                                                                           | FPGA Spartan 31                                               |

| (Pathak et al., 2018)               | IIR Notch/anti-notch                                                                          | N/A*                    | N/A*                                                                                           | FPGA Zynq                                                     |

| (ECG, 2018)                         | Adaptive Dual<br>Threshold Filter                                                             | MIT-BIH arrhyth-<br>mia | High Frequency Noise                                                                           | N/A*                                                          |

| (Venkatesan et al., 2019)           | LMS Adaptive Filter                                                                           | N/A*                    | White Gaussian Noise                                                                           | FPGA Virtex 5                                                 |

| (Sohal & Jain, 2019)                | FIR filter                                                                                    | MIT-BIH arrhyth-<br>mia | Electromyography Noise<br>and BLW Noise                                                        | FPGA Zynq                                                     |

| (Thirrunavukkarasu et al.,<br>2021) | Kaiser FIR filter                                                                             |                         | Noise Occurs Due to<br>Outer Surface of The<br>Thermal and Electro-<br>magnetics Field         | FPGA                                                          |

| (Mejhoudi et al., 2021)             | Adaptive Dual<br>Threshold Filter                                                             | MIT-BIH arrhyth-<br>mia | High-Frequency Noises,<br>Electromyogram Noises,<br>Power Line Interferences                   | FPGA Intel<br>Altera                                          |

| (Patel & Shah, 2022)                | Multiband FIR Filter                                                                          | Physionet               | Baseline Wandering, Mo-<br>tion Artefacts,<br>High Frequency Noises<br>Power Line Interference | FPGA Spartan 3                                                |

| (Sohal & Jain, 2022)                | Linear Windowing<br>Techniques and<br>Non-Linear DWT                                          | MIT-BIH arrhyth-<br>mia | Low-Frequency<br>Noise and High-<br>Frequency Noise                                            | different FPGA<br>boards (Virtex<br>Kintex, and<br>Zedboards) |

| (Elbedwehy et al., 2022)            | Single-Node Reser-<br>voir Computing<br>architecture, based<br>on Recurrent Neural<br>Network | MIT-BIH arrhyth-<br>mia | Electromyogram (EMG)<br>Nois, Power Line Inter-<br>ference (PLI) Noise                         | FPGA Artix-7                                                  |

| (Shanmugaraja et al., 2023)         | LMS adaptive filter                                                                           | N/A*                    | White Gaussian Noise                                                                           | FPGA Vertex 5                                                 |

| (Vaishnavi et al., 2023)            | LMS<br>Adaptive Filter                                                                        | MIT-BIH                 | Baseline Wander Noise                                                                          | N/A*                                                          |

| (Gon & Mukherjee, 2023)             | Lifting-Based<br>Wavelet                                                                      | MIT-BIH arrhyth-<br>mia | N/A*                                                                                           | FPGA Nexy<br>4DDR                                             |

| (Boumehrez et al., 2023)            | Lifting 9/7 Wavelet<br>FBs                                                                    | N/A*                    | N/A*                                                                                           | FPGA Altera                                                   |

| Table | 1: | Summarizes | the | different | $\mathbf{noise}$ | elimination  | approaches | utilized | by | research | iers i | n re | $\operatorname{cent}$ |

|-------|----|------------|-----|-----------|------------------|--------------|------------|----------|----|----------|--------|------|-----------------------|

|       |    |            |     |           | studie           | s for the EC | G signal   |          |    |          |        |      |                       |

Ma et al. (2016) proposed an R wave detection algorithm using lifting wavelet and differential operations and implemented it on an FPGA. The algorithm ensured low computational complexity and high accuracy, making it suitable for portable electrocardiogram monitoring devices. Evaluation on databases like MIT-BIH ST Change, MIT-BIH Arrhythmia, and Supraventricular Arrhythmia databases, achieved high accuracy rates of over 99.8% in MATLAB simulations and an average recognition rate of 99.68% in FPGA experiments. The algorithm occupied minimal FPGA resources, according to the resource estimation report.

Abdullah and Abd (2016) developed a reliable FPGA-based ECG analysis system for accurate QRS complex determination and beat-to-beat interval extraction. The system included a VHDL-based R peak detection module implemented using Xilinx ISE 14.6 and simulated with MATLAB System Generator. Performance testing used MITBIH Arrhythmia ECG database. FPGA system handled preprocessing, feature extraction, and classification with validated results.

Zhang et al. (2017) introduced an algorithm based on wavelets for detecting QRS complexes from ECG signals. Their method outperformed the Pan-Tompkins algorithm in terms of resource consumption and design simplicity. The algorithm enabled real-time QRS complex detection, suitable for telemonitoring high-risk cardiac patients.

Kumar and Chari, (2018) presented an efficient FPGA architecture for ECG R-peak detection by combining Shannon energy and Hilbert transform. The smooth Shannon energy envelope is obtained through extraction and filtering. The Hilbert transform accurately locates the R-peak, and FFT techniques improve performance. The technique achieved 99.86% accuracy, 99.95% sensitivity, and 99.90% positive predictivity with the MIT-BIH arrhythmia database.

Martínez-Suárez and Alvarado-Serrano (2019) developed a prototype ambulatory ECG monitoring system that acquires and stores 3 leads with real-time R-wave detection using a spline wavelet transform on an FPGA. The system included a 4-channel ECG front end ADS1294, 16 GB micro SD memory, and Artix-7 FPGA with a 200 Hz bandwidth, 112 dB CMRR, 0.76  $\mu V$  resolution, and 125 mA average current consumption lasting at least 30 hours. Evaluating the R wave detection algorithm on the VF lead with 30-minute records of 5 resting subjects, it achieved 99.4% accuracy. The system provided real-time beat-to-beat heart rate measurements, making it valuable for long-term ECG monitoring applications.

Nez-Suárez and Alvarado-Serrano (2019) proposed a module that detected R waves and calculated beat-to-beat RR intervals using continuous spline wavelet transform. Tested on the Basys 3 development card with an Artix-7 FPGA, the module achieved over 90% accuracy in analyzing five 30-minute and one 24-hour ECG recordings. It enabled heart rate variability analysis in long and short ECG recordings when implemented on an FPGA.

Talukder et al. (2020) introduced a real time QRS detection method utilizing Integer Haar Wavelet Transform. The algorithm was implemented on a Digilent Nexys 4 FPGA board, making it suitable for medical equipment and IoT systems. They simplified the hardware architecture by approximating floating point arithmetic to integer arithmetic. An architecture was demonstrated through simulation and hardware testing, achieving an error percentage of less than 1.4% in RR interval computation and 98.76% accuracy in QRS detection. The synthesis of the architecture using 130 nm technology resulted in only 0.717% leakage power.

Meddah et al. (2020) presented an FPGA-based system for ECG monitoring and arrhythmia detection. It used the Tompkins and Pan algorithm for QRS detection and was optimized for the Spartan 3E FPGA board. Comparative studies validated its effectiveness and reliability, achieving high sensitivity and accuracy.

Chen et al. (2020) proposed a lightweight QRS detection algorithm employing adaptive threshold techniques. It achieved high sensitivity, positive predictivity, and accuracy. The algorithm's effectiveness was demonstrated using MIT-BIH databases, making it suitable for wearable heart rate monitoring and automatic ECG analysis.

García-Limón et al. (2021) created an FPGA-based prototype for ambulatory ECG monitoring, acquiring and storing 3 leads for real-time measurements. The system utilized a Xilinx Artix-7 FPGA, an ADS1294 circuit for lead acquisition, and a micro-SD memory for storage. It met the required electrocardiograph characteristics, including a bandwidth of 0.05-100 Hz and a CMRR of at least 80 dB.

Wei et al. (2021) proposed a method to suppress baseline drift in ECG acquisition using a digital-analog mixing approach. They presented an adaptive threshold-based feature recognition algorithm for real-time analysis of ECG signal morphology. The system achieved high accuracy in detecting QRS waves (over 99%) and T waves (94%). The paper integrated analog and digital signal processing, along with PCB drawing, to automatically extract, process, and detect user ECG signals. The Savitzky-Golay (SG) filter effectively suppressed low-frequency baseline drift and noise in the digital ECG signal.

Ganatra and Vithalani (2022) proposed an approach for analyzing ECG signals using FPGA technology, focusing on morphological feature extraction. The architecture utilized GSST and a detrended fluctuation analyzer to extract QRS complexes and P-waves. QRS regions are accurately localized using a correntropy envelope, and true P-waves are detected through an adaptive heuristic framework. Root mean square error estimation is employed to guide adaptive thresholding, enabling accurate T-wave measurements. Utilizing the Virtex 7 FPGA platform, the implemented architecture underwent a comprehensive comparative study with other feature descriptors to assess its performance and efficiency.

Malathi and Vijay Kumar (2023) proposed a high-performance, low-complexity QRS detector design called QRS-MoMaMeMi-MOA. It utilized the MoMaMeMi filter optimized with the Mayfly optimization algorithm to suppress high-frequency noise and remove baseline wander in ECG signals. The filter outperforms existing methods such as QRS-HD-MaMeMi, QRS-KF-ATA, and QRS-CAF in terms of accuracy and detection error rates. The filter design is implemented on FPGAs.

| (Reference)                                    | Fiducial Points | Method for Detection                                                                                                                       | Kit Type        |

|------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| (Ma et al., 2016)                              | R-Wave          | Lifting Wavelet                                                                                                                            | FPGA Altera     |

| (Abdullah & Abd, 2016)                         | R-R Interval    | FPGA-Based ECG Analysis<br>System                                                                                                          | FPGA Spartan 3A |

| (Zhang et al., 2017)                           | QRS Complex     | Integer Haar Transform                                                                                                                     | FPGA Cyclone    |

| (Aravind Kumar & Manju-<br>natha Chari, 2018)  | R-Wave          | Method combines a Band-<br>pass filter, first-order dif-<br>ferentiation process, Shan-<br>non energy extraction, and<br>Hilbert Transform | FPGA Vertex 5   |

| (Martínez-Suárez & Alvarado-<br>Serrano, 2019) | R-Wave          | Prototype Ambulatory ECG<br>Monitoring System                                                                                              | FPGA Artix-7    |

| (Nez-Suárez & Alvarado-<br>Serrano, 2019)      | R-Wave          | Continuous Wavelet Trans-<br>form                                                                                                          | N/A*            |

| (Talukder et al., 2020)                        | QRS Complex     | Integer Haar Wavelet Trans-<br>form                                                                                                        | FPGA Artix-7    |

| (Meddah et al., 2020)                          | QRS Complex     | FPGA-based system for<br>ECG signal monitoring<br>and cardiac arrhythmia<br>detection                                                      | FPGA Nexys 2    |

| (A. Chen et al., 2020)                         | QRS Complex     | ET and PD Controlled<br>Threshold Strategy                                                                                                 | FPGA Altera     |

| (García-Limón et al., 2021)                    | QRS, T-Wave     | Prototype of an Ambulatory<br>Long-Term ECG Monitor-<br>ing System                                                                         | FPGA Artix-7    |

| (Wei et al., 2021)                             | QRS, T-Wave     | SG Filter                                                                                                                                  | FPGA Altera     |

| (Ganatra & Vithalani, 2022)                    | QRS, P-Wave     | Generalized Synchros queez-<br>ing Transform, Correntropy<br>Function and Adaptive<br>Heuristic Framework                                  | FPGA Vertex 7   |

| (Malathi & Vijay Kumar, 2023)                  | QRS Complex     | Modified MaMeMi Filter                                                                                                                     | FPGA Zynq       |

| (Yan et al., 2023)                             | R-Wave          | FIR , High-Order Adaptive<br>Median Filter                                                                                                 | FPGA Altera     |

| (García Limón et al., 2023)                    | RT interval     | Continuous Wavelet Trans-<br>form                                                                                                          | FPGA Artix-7    |

Table 2: Summary of various ECG feature extraction approaches

Yan et al. (2023) focused on automatic detection of QRS wave groups in ECG signals for data analysis. MIT-BIH database and human ECG data were used. A high-order FIR low-pass filter and Shannon energy algorithm are applied to process the data and minimize noise. The proposed method accurately extracted R-waves and controlled the left ventricular assist device (LVAD) for blood pumping. Feasibility was tested with normal and abnormal ECG signals using the R-R interval and threshold method.

García Limón et al. (2023) implemented algorithms using the CWT with splines in an ambulatory ECG monitor prototype. The prototype features an ADS1294 analog-digital converter, Xilinx XC7A35T-ICPG236C FPGA Artix-7, LCD, and 16 GB micro-SD memory. The FPGA algorithm enabled real time detection of various T wave and QRS complex morphologies, facilitating heart rate and RT interval analysis. Table 2. presents a compilation of approaches that extract features from the ECG signal.

#### 2.3 Stage 3: Classification

After noise filtration and feature engineering, the ECG signals are categorized into various classes based on detected fiducial points and the specific issue being addressed. This section covers literature approaches for ECG signal classification with hardware implementation.

Abubakar et al. (2018) presented a patient-specific processor for classifying shockable cardiac arrhythmia without using machine learning. The processor included an efficient hardware-based engine for extracting a reduced set of five features. A patient-specific, adaptive thresholding engine was implemented for robust peak and interval detection, along with simplified decision logic for real time arrhythmia discrimination. With a specificity of 99.75% and an average sensitivity of 98.66%, the SCAD processor achieves high classification accuracy. Additionally, consumed low power, with a classification energy consumption of  $0.89\mu J$ . The system is designed for wearable defibrillators, providing immediate response time and continuous monitoring of SCA and non-SCAs. The paper compared the proposed system with state-of-the-art works, highlighting its comparable performance and advantages.

Sharabaty et al. (2018) proposed a classification system based on FPGA for identifying

various heart malfunctions using standard ECG features. The system was implemented on Xilinx Spartan 3AN FPGA using Labview and Verilog. Two classifiers, NVG-RAM and TD weightless neural network, were used for decision-making in the system. The NVG-RAM and TD classifiers were compared to assess their suitability for the ECG classification system. Experimental data demonstrated a 100% PCC for heart conditions with the NVG-RAM classifier and a 98.84% PCC with the TD classifier.

Alfaro-Ponce et al. (2019) developed an algorithm using a continuous neural network for automatic detection of arrhythmias. The algorithm was implemented on FPGA with fixed point arithmetic. Validation achieved 93.80% accuracy and 98% average sensitivity using fivefold cross-validation on the entire set of EKG signal samples. CoNN was introduced as a real-time classifier, representing an early attempt to directly classify arrhythmias using EKG signals.

Saadi et al. (2019) developed a system that utilizes Xilinx System Generator blocks to implement an ECG-neuro classifier on an FPGA kit. They employed an approximate linear phase BLWDF to extract the QRS complex from the ECG signal. The classifier categorized ECG signals from European databases into four heart disease classes: Normal, RBBB, LVH, and LBBB. The neural network training process included using the Matlab toolbox to acquire the necessary weights and biases. VHDL translation of the models helped measure chip resource usage and calculate the maximum operating frequency.

Zairi et al. (2020) developed an FPGA-based arrhythmia recognition system using an artificial neural network. They optimized the software-based diagnostic approach to minimize the FPGA energy consumption and prototype size. The classification method involved waveletbased feature extraction, multilayer perception (MLP) classification, and class decision. The methodology was implemented using the Nexys4 Artix7 evaluation kit and XSG for DSP. Performance comparison with MATLAB floating point validated the FPGA fixed point architecture as a customized mobile classifier for real-time patient monitoring.

Liu et al. (2020) utilized DWT for feature extraction from ECG signals, specifically using the "db2" wavelet's approximate coefficient as feature vectors. ECG signal classification employed the SVM algorithm, known for effective classification. The SVM circuit was generated through high-level synthesis (HLS), optimizing it through source code rewriting and additional directives. The system was implemented on the Xilinx ZYNQ SoC, integrating the processing system and programmable logic on a single chip. The system achieved 98.7% classification accuracy and a real-time classification time of 280 ps per heartbeat.

Lu et al. (2021) used a 1-D CNN structure with a GAP layer for ECG beats classification. The architecture was designed to meet the specific requirements of this task, incorporating data reuse strategies to optimize memory access and increase parallelism. The Relu function implementation was moved to the processing unit to reduce hardware resource consumption. The irregular GAP operation was implemented without additional overhead. The trained parameters were saved in weight and bias RAM before making predictions. Data Scatter was used for data distribution and padding. The PU array ran in a pipeline to generate efficient calculation results, which were then quantized using a Bit-width Converter.

Lee et al. (2021) introduced a system for real time ECG diagnosis using hardware accelerators and an approximated template-based algorithm. This personalized approach improves detection rates and reduces memory usage compared to existing methods. The algorithm adapts to individual reference beats, allowing personalized diagnosis for each person's signal. Experimental results demonstrated a significant reduction in diagnosis time, with an 89.96% shorter execution time compared to software when diagnosing ECG signals from five individuals containing 1987 beats. Additionally, a signal processing unit is introduced for real-time ECG data processing.

Xing et al. (2022) introduced a power resource of recognition of heartbeat-ECG by model of spiking neural networks and, moreover, operated the attention mechanism as splitted in channels. The optimized model was the most accurate, low power consumption, and it was possible to track the ECG signal variations in real time, thus, effectively detecting anomalies in ECG signals.

Chen and Wong (2022) introduced neuromorphic based standardization methodology to classify ECG signal utilizing spike timing dependent plasticity. They really made ECG classifier on a FPGA-based neuromorphic circuit with the use of the efficient resource occupation.

Dal and Aşkar (2022) showed their FPGA classifier based on ANN architecture that did not require the necessity of using a feature extraction method. ANN was being developed using the MITBIH arrhythmia dataset by applying training and validation. A mathematical model of the feed-forward network was developed using Verilog HDL on Xilinx Zybo FPGA. Network parameters, including weights and biases, were converted from 32-bit floating-point to 8-bit fixed-point numbers for efficient FPGA mapping. The ANN model achieved approximately 97% accuracy during training. The entire procedure was completed within 232 clock cycles, showcasing the efficiency of the approach.

Lu et al. (2022) proposed a CNN accelerator for ECG classification using tile-first dataflow and a specialized data compression format. The system architecture has a central controller with an FSM for instruction fetching and control signal provision. The PE array consisted of four cascade PE structures for addition and multiplication operations, generating partial sums of a tile. The pooling module supported various operations such as average pooling, max pooling, and global average pooling on the calculation results. The network employs 16-bit data quantization, which maintains accuracy for ECG classification with minimal loss.

Ku et al. (2023) proposed a high-performance AIA for arrhythmia classification on ECG using an efficient 1DCNN. The architecture achieved real time low-power consumption and high-accuracy classification. It reduced memory access time by 29x and latency by 22.5x compared to a single MAC operation. The hardware implementation on Xilinx PYNQ-Z2 had small latency and provided high performance. Software simulation achieved accuracies of 97.3% and 98.3%, while hardware implementation with quantization and pruning achieved accuracies of 96.6% and 96.5%.

Chang et al. (2023) developed a smart clothing system for the automatic detection of cardiovascular diseases (CVDs) in daily life. An FPGA-based ECG analysis module implemented a CVD detection algorithm for real-time data extraction and analysis. The fabric of the smart clothing was coated with graphene oxide to improve conductivity and enable non-contact sensing. ECG was recognized as an important diagnostic technique, providing detailed information about cardiac activity during muscle depolarization and repolarization.

Lu et al. (2023) presented an LMA network for ECG classification, tailored to the signal characteristics and classification model requirements. An accelerator that employs multiple channels in parallel and utilizes output data reuse has successfully achieved efficient pipeline processing and low-power acceleration. Deployed on Xilinx's ZYNQ-7100 platform, the accelerator achieves 116.7 GOPs throughput with 6.67W power consumption. It boasted a hardware resource utilization rate of 0.33 GOPS/DSP and 2.85 GOPS/kLUT, surpassing general CPUs/GPUs in hardware utilization and energy efficiency. This accelerator met the demands of high-performance, low-power intelligent terminal devices. These different classification methods are summarized in Table 3.

## 3 Trend Directions of Researchers

This section provides an overview of the major trends identified by prominent researchers in ECG real-time processing stages as a reference and starting point for new researchers (Azzouz et al., 2024; Brindha & Manjula, 2023; Chinmayi & Padmaja, 2023; Manga et al., 2024; Shekhawat et al., 2024; Sinha & Kar, 2024; Swetha & Ramakrishnan, 2024; Thannoon & Hashim, 2024; Yang et al., 2024).

• LMS Adaptive Filter for denoising.

| (Reference)                 | Algorithm                  | Database             | Platform Type    |

|-----------------------------|----------------------------|----------------------|------------------|

| (Abubakar et al., 2018)     | SCA processor              | ECG-ID, MIT-         | FPGA             |

| (1150504441 et al., 2010)   | Seri processor             | arrhythmia           | 11 OII           |

| (Sharabaty et al., 2018)    | TD, NVG-RAM                | MIT-BIH arrhythmia   | FPGA Spartan 3AN |

| (Alfaro-Ponce et al., 2019) | Continuous Neural Network  | MIT-BIH Arrhythmia   | FPGA Zinq        |

| (Saadi et al., 2019)        | BLWDF                      | European ST-T and QT | FPGA Spartan 6   |

| (Zairi et al., 2020)        | ANN                        | Physiobank           | FPGA Artix7      |

| (Liu et al., 2020)          | DWT and SVM                | MIT-BIH arrhythmia   | FPGA Zynq        |

| (J. Lu et al., 2021)        | Convolutional Neural Net-  | MIT-BIH arrhythmia   | FPGA Zynq        |

|                             | work                       |                      |                  |

| (Lee et al., 2021)          | Energy-Efficient FPGA Ac-  | MIT-BIH arrhythmia   | FPGA Alveo       |

|                             | celerator                  | -                    | U200             |

| (Xing et al., 2022)         | SNN                        | MIT-BIH arrhythmia   | FPGA             |

| (D. R. Chen & Wong, 2022)   | neuromorphic methods       | MIT-BIH Arrhythmia   | FPGA Zedboard    |

| (Dal & Aşkar, 2022)         | ANN                        | MIT-BIH Arrhythmia   | FPGA Zybo        |

| (J. Lu et al., 2022)        | CNN                        | N/A*                 | FPGA Zynq        |

| (Ku et al., 2023)           | 1DCNN                      | MIT-BIH Arrhythmia   | FPGA PYNQ-Z2     |

| (Chang et al., 2023)        | Smart Clothing System      | MIT-BIH arrhythmia,  | FPGA Artix-7     |

|                             |                            | MIT-BIH AF, and      |                  |

|                             |                            | MGHMF waveform       |                  |

| (T. Lu et al., 2023)        | Multi-Scale Attention Net- | PTB-XL dataset       | FPGA Zynq        |

|                             | work                       |                      |                  |

Table 3: Summary of various ECG classification approaches

- Adaptive Filter Incorporating Systolic Architecture to remove PLI noise from ECG signals.

- Lifting-Based Wavelet Denoising.

- combination of particle swarm optimisation and wavelet transform for denoising.

- Generalized Synchrosqueezing Transform, Correntropy Function and Adaptive Heuristic Framework for denoising.

- Arithmetic optimised APT-VDF using reusable Vedic multiplier with simplified combinational logics for denoising.

- An adaptive and effective signed error normalized least mean square algorithm (SE-NLMS) or Mixed Noise Removal and Classification

- Integer Haar Wavelet and EMD Algorithm for feature extraction.

- A-CLT and digital fractional order differentiation for QRS-complex identification.

- Modified MaMeMi Filter Optimized with Mayfly Optimization Algorithm for QRS Detection.

- A WOA optimized fractional-order digital differentiator for QRS complex detection.

- Wavelet-Transform for RT Interval Measurements.

- Binarized spiking neural network optimized with momentum search algorithm for arrhythmia detection and classification.

- SVM classifier for arrhythmia detection.

- Convolutional Neural Network Accelerator for Wearable ECG Classification.

- Accelerating CNN Inference for ECG Classification.

- Real-time ECG monitoring and diagnosis through IoT.

# 4 Comparative Study

To highlight the contribution of this review compared to related review papers, a comparison with other relevant reviews in the field is presented. Given the extensive research conducted on ECG, numerous survey papers have been published. This review carefully selected reputable papers for a comparative analysis, as shown in Table 4. Notably, this survey distinguishes itself by focusing on research tools employed at each stage of the real-time ECG signal analysis process. This structure offers a comprehensive and stage-based approach to ECG research, serving as a valuable resource for both new and experienced researchers in this competitive field.

|                                                                    | ECG Signal pro                         | cessing stages            |                                |                         |                                                                                                                |

|--------------------------------------------------------------------|----------------------------------------|---------------------------|--------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------|

| (Reference)                                                        | Stage1: Prepr<br>cessing (Deno<br>ing) | is- Feature<br>Extraction | Stage3:<br>Classifica-<br>tion | Real-Time<br>processing | Focus Area                                                                                                     |

| (Iqbal, Wah, &<br>Rehman, 2018)                                    | No                                     | Yes                       | Yes                            | No                      | Feature<br>Extraction                                                                                          |

| (Satija, Ramku-<br>mar, & Manikan-<br>dan, 2018)                   | Yes                                    | Yes                       | Yes                            | No                      | Denoising<br>Classification                                                                                    |

| (Lamba & Rawal,<br>2019)                                           | No                                     | Yes                       | Yes                            | No                      | Classification                                                                                                 |

| (Chatterjee,<br>Thakur, Yadav,<br>Gupta, & Raghu-<br>vanshi, 2020) | Yes                                    | No                        | No                             | No                      | Denoising                                                                                                      |

| (Sahoo, Dash, Be-<br>hera, & Sabut,<br>2020)                       | Yes                                    | Yes                       | Yes                            | No                      | Arrhythmia<br>Detection                                                                                        |

| (Fikri et al., 2021)                                               | No                                     | No                        | Yes                            | No                      | Classification                                                                                                 |

| (Xiao et al., 2023)                                                | Yes                                    | Yes                       | Yes                            | No                      | Arrhythmia<br>Classifica-<br>tion                                                                              |

| (Talwar & Cecil, 2023)                                             | Yes                                    | No                        | No                             | No                      | Denoising                                                                                                      |

| (Singh & Krish-<br>nan, 2023)                                      | No                                     | Yes                       | No                             | No                      | Feature<br>Extraction                                                                                          |

| (Ardeti, Kolluru,<br>Varghese, &<br>Patjoshi, 2023)                | Yes                                    | Yes                       | Yes                            | Yes                     | Processing<br>Methods:<br>Form Tra-<br>ditional To<br>AI                                                       |

| Our article                                                        | Yes                                    | Yes                       | Yes                            | Yes                     | 3-Stages<br>ECG<br>Real-Time<br>Processing<br>Denoising,<br>Feature<br>Extrac-<br>tion,<br>Classifica-<br>tion |

Table 4: Comparative summary of ECG Review papers

# 5 Conclusion

Electrocardiography (ECG) is a crucial diagnostic tool for identifying irregularities in the heart's electrical activity, which can signify underlying abnormalities in heart function. This paper presented a review of real time ECG signal processing. In general, there are three stages of ECG processing, namely, preprocessing stage, feature extraction stage and classification stage, Most ECG research falls into one or more of the three processing stages outlined in this model. This paper guides researchers through the vast ECG literature, highlighting how signals progress through processing stages and what each stage entails. Our survey compiled a diverse range of

recently published ECG analysis methods, conveniently presented in a table for easy comparison. A striking observation from our survey: the vast majority of researchers leverage the MIT-BIH dataset for evaluating their one-dimensional ECG analysis and classification techniques. This review's insights illuminate the path for future researchers, empowering them to bridge knowledge gaps and conquer challenges in this growing field.

#### References

- Saadi, O.N., Abdulkader, Z.N., & Abdul-Jabbar, J.M. (2019, February). Implementation of ECG Classification Xilinx System Generator. In 2019 2nd International Conference on Electrical, Communication, Computer, Power and Control Engineering (ICECCPCE) (pp. 1-6). IEEE.

- Abdulla, L.A., Al-Ani, M.S. (2020). A review study for electrocardiogram signal classification. UHD Journal of Science and Technology, 4(1), 103-117.

- Abdullah, H.N., Abd, B.H. (2016, June). A simple FPGA system for ECG RR interval detection. In 2016 IEEE 11th Conference on Industrial Electronics and Applications (ICIEA) (pp. 1379-1382). IEEE.

- Abubakar, S.M., Khan, M.R., Saadeh, W., & Altaf, M.A.B. (2018, November). A wearable auto-patient adaptive ECG processor for shockable cardiac arrhythmia. In 2018 IEEE Asian Solid-State Circuits Conference (A-SSCC) (pp. 267-268). IEEE.

- Al-Khammasi, S., Aboalayon, K. A., Daneshzand, M., Faezipour, M., & Faezipour, M. (2016, October). Hardware-based FIR filter implementations for ECG signal denoising: A monitoring framework from industrial electronics perspective. In 2016 Annual Connecticut Conference on Industrial Electronics, Technology & Automation (CT-IETA) (pp. 1-6). IEEE.

- Alfaro-Ponce, M., Chairez, I., & Etienne-Cummings, R. (2019). Automatic detection of electrocardiographic arrhythmias by parallel continuous neural networks implemented in FPGA. *Neural Computing and Applications*, 31, 363-375.

- Aravind Kumar, M., Manjunatha Chari, K. (2018). Efficient FPGA-based VLSI architecture for detecting R-peaks in electrocardiogram signal by combining Shannon energy with Hilbert transform. *IET Signal Processing*, 12(6), 748-755.

- Ardeti, V.A., Kolluru, V.R., Varghese, G.T., & Patjoshi, R.K. (2023). An overview on stateof-the-art electrocardiogram signal processing methods: Traditional to AI-based approaches. *Expert Systems with Applications*, 217, 119561.

- Azzouz, A., Bengherbia, B., Wira, P., Alaoui, N., Souahlia, A., Maazouz, M., & Hentabeli, H. (2024). An efficient ECG signals denoising technique based on the combination of particle swarm optimisation and wavelet transform. *Heliyon*.

- Boumehrez, F., Sahour, A., Maamri, F., & Djellab, H. (2023, April). Lifting of the 9/7 Wavelet Filter Bank for ECG Signal Analysis Implementation Based on FPGA Target. In 2023 IEEE International Conference on Advanced Systems and Emergent Technologies (IC\_ASET) (pp. 01-05). IEEE.

- Brindha, G.S., Manjula, J. (2023, April). FPGA-Based ECG signal analysis for arrhythmia detection system using SVM classifier. In AIP Conference Proceedings (Vol. 2603, No. 1). AIP Publishing.

- Chang, W.-T., Lin, B.-S., Chen, Y.-L., Chen, H.-Y., Liu, C., Hwang, Y.-T., & Lin, B.-S. (2023). Design of Smart Clothing With Automatic Cardiovascular Diseases Detection. *IEEE Transactions on Human-Machine Systems*.

- Chatterjee, S., Thakur, R.S., Yadav, R.N., Gupta, L., & Raghuvanshi, D.K. (2020). Review of noise removal techniques in ECG signals. *IET Signal Processing*, 14(9), 569-590.

- Chen, A., Zhang, Y., Zhang, M., Liu, W., Chang, S., Wang, H., . . . Huang, Q. (2020). A real time QRS detection algorithm based on ET and PD controlled threshold strategy. *Sensors*, 20(14), 4003.

- Chen, D.R., Wong, Y.C. (2022). Neuromorphic solutions: digital implementation of bio-inspired spiking neural network for electrocardiogram classification. *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, 27(1), 528-537.

- Chinmayi, K., Padmaja, M. (2023, September). VLSI implementation of ECG feature extraction using Integer Haar Wavelet and EMD Algorithm. In 2023 First International Conference on Cyber Physical Systems, Power Electronics and Electric Vehicles (ICPEEV) (pp. 1-6). IEEE.

- Dal, B., Aşkar, M. (2022, October). Fixed-point FPGA Implementation of ECG Classification using Artificial Neural Network. In 2022 Medical Technologies Congress (TIPTEKNO) (pp. 1-4). IEEE.

- ECG, A.D.T.F.B. (2018). Real-time hardware architecture of the adaptive dual threshold filter based ECG signal denoising. Journal of Theoretical and Applied Information Technology, 96(14).

- Elbedwehy, A.N., El-Mohandes, A.M., Elnakib, A., & Abou-Elsoud, M.E. (2022). FPGAbased reservoir computing system for ECG denoising. *Microprocessors and Microsystems*, 91, 104549.

- Fikri, M.R., Soesanti, I., & Nugroho, H.A. (2021). ECG signal classification review. IJITEE International Journal of Information Technology and Electrical Engineering, 5(1), 15-20.

- Gaikwad, K., Chavan, M. (2016). Design and Implementation Digial Chebyshev Type II Filter Using XSG for Noise Reduction ECG Signal. International Journal of Engineering Research and Application, SSN, 2248-9622.

- Gaikwad, K.M., Chavan, M. (2018). Elliptic filter implementation using Xilinx system generator for processing of ECG signal. Communications on Applied Electronics, 7(12), 25-29.

- Ganatra, M.M., Vithalani, C.H. (2022). A novel morphological feature extraction approach for ECG signal analysis based on generalized synchrosqueezing transform, correntropy function and adaptive heuristic framework in FPGA. Journal of Circuits, Systems and Computers, 31(18), 2250312.

- García-Limón, J.A., Martínez-Suárez, F., & Alvarado-Serrano, C. (2021). Prototype of an Ambulatory Long-Term ECG Monitoring System for Real Time Detection of QRS Complex and T Wave End Based on FPGA. In 2021 18th International Conference on Electrical Engineering, Computing Science and Automatic Control (CCE) (pp. 1-6). IEEE.

- García Limón, J.A., Martínez-Suárez, F., & Alvarado-Serrano, C. (2023). Implementation of wavelet-transform-based algorithms in an FPGA for heart rate and rt interval automatic measurements in real time: application in a long-term ambulatory electrocardiogram monitor. *Micromachines*, 14(9), 1748.

- Gon, A., Mukherjee, A. (2023). Design and FPGA Implementation of an Efficient Architecture for Noise Removal in ECG Signals Using Lifting-Based Wavelet Denoising. In 2023 11th International Symposium on Electronic Systems Devices and Computing (ESDC).

- Guyton, A.C. (2006). Text Book of Medical Physiology. China.

- Iqbal, U., Wah, T.Y., & Rehman, M.H.U. (2018). Usage of model driven environment for the classification of ECG features: A systematic review. *IEEE Access*, 6, 23120-23136.

- Ku, M.-Y., Zhong, T.-S., Hsieh, Y.-T., Lee, S.-Y., & Chen, J.-Y. (2023). A high performance accelerating CNN inference on FPGA with arrhythmia classification. In 2023 *IEEE 5th International Conference on Artificial Intelligence Circuits and Systems* (AICAS).

- Lamba, P., Rawal, K. (2019). A survey of algorithms for feature extraction and feature classification methods. In 2019 International Conference on Automation, Computational and Technology Management (ICACTM).

- Lee, D., Lee, S., Oh, S., & Park, D. (2021). Energy-efficient FPGA accelerator with fidelitycontrollable sliding-region signal processing unit for abnormal ECG diagnosis on IoT edge devices. *IEEE Access*, 9, 122789-122800.

- Liu, Y., Dong, L., Zhang, B., Xin, Y., & Geng, L. (2020). Real time ECG classification system based on DWT and SVM. In 2020 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA).

- Lu, J., Liu, D., Cheng, X., Wei, L., Hu, A., & Zou, X. (2022). An efficient unstructured sparse convolutional neural network accelerator for wearable ECG classification device. *IEEE Trans*actions on Circuits and Systems I: Regular Papers, 69(11), 4572-4582.

- Lu, J., Liu, D., Liu, Z., Cheng, X., Wei, L., Zhang, C., ... Liu, B. (2021). Efficient hardware architecture of convolutional neural network for ECG classification in wearable healthcare device. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 68(7), 2976-2985.

- Lu, T., Zhao, B., Xie, M., & Ma, Z. (2023). FPGA Design and Implementation of ECG Classification Neural Network. In 2023 IEEE 3rd International Conference on Computer Communication and Artificial Intelligence (CCAI).

- M Abdul-Jabbar, J., Waleed Hamad, R. (2014). Fuzzy classification of ECG signals using A QRS-like FIR filter bank with lattice structures. *Al-Rafidain Engineering Journal* (AREJ), 22(2), 1-12.

- Ma, Y., Li, T., Ma, Y., & Zhan, K. (2016). Novel real-time FPGA-based R-wave detection using lifting wavelet. *Circuits, Systems, and Signal Processing*, 35, 281-299.

- Malathi, S., Vijay Kumar, P. (2023). A high-performance low complex design and implementation of QRS detector using modified MaMeMi filter optimized with Mayfly optimization algorithm. *Journal of Circuits, Systems and Computers, 32*(4), 2350056.

- Manga, N. A., Pradeep Kumar, G., & Satyanarayana Tallapragada, V. (2024). FPGA design of arithmetic optimised APT-VDF using reusable Vedic multiplier with simplified combinational logics for medical signal denoising. *International Journal of Electronics*, 111(1), 64-85.

- Martínez-Suárez, F., & Alvarado-Serrano, C. (2019). Prototype of an ambulatory ECG monitoring system with R wave detection in real time based on FPGA. In 2019 16th International Conference on Electrical Engineering, Computing Science and Automatic Control (CCE).

- Meddah, K., Talha, M.K., Zairi, H., Nouah, M., Hadji, S., Ait, M.A., ... Cherrih, H. (2020). FPGA implementation system for QRS complex detection. *Biomedical Engineering: Applica*tions, Basis and Communications, 32(1), 2050005.

- Mejhoudi, S., Jenkal, R.L.W., Saddik, A., & Satie, A.E.O. (2021). Hardware architecture for adaptive dual threshold filter and discrete wavelet transform based ECG signal denoising. *International Journal of Advanced Computer Science and Applications*, 12(11).

- Nez-Suárez, F. M., Alvarado-Serrano, C. (2019). VHDL module for the R wave detection in real time using continuous wavelet transform. In 2019 16th International Conference on Electrical Engineering, Computing Science and Automatic Control (CCE).

- Patel, V., Shah, A. (2022). Denoising electrocardiogram signals using multiband filter and its implementation on FPGA. Serbian Journal of Electrical Engineering, 19(2), 115-128.

- Pathak, V., Nanda, S.J., Joshi, A.M., & Sahu, S.S. (2018). High speed implementation of Notch/Anti-notch IIR filter on FPGA. In 2018 15th IEEE India Council International Conference (INDICON).

- Roth, G.A., Mensah, G.A., & Fuster, V. (2020). *The global burden of cardiovascular diseases and risks: a compass for global action* (Vol. 76, pp. 2980-2981). American College of Cardiology Foundation Washington DC.

- Sahoo, S., Dash, M., Behera, S., & Sabut, S. (2020). Machine learning approach to detect cardiac arrhythmias in ECG signals: A survey. *Irbm*, 41(4), 185-194.

- Satija, U., Ramkumar, B., & Manikandan, M.S. (2018). A review of signal processing techniques for electrocardiogram signal quality assessment. *IEEE Reviews in Biomedical Engineering*, 11, 36-52.

- Shanmugaraja, T., Ruba, M., Priya, V.S., Venkatesh, T., Supriya, M., & Nallamuthu, M. (2023). ECG noise elimination using an FPGA version of a modified error normalized LMS adaptive filter. AIP Conference Proceedings.

- Sharabaty, H., Ahkam, I., & Baba, A. (2018). FPGA-Based Multi Heart Diseases Classification System with the Aid of LabVIEW. In 2018 2nd International Symposium on Multidisciplinary Studies and Innovative Technologies (ISMSIT).

- Shekhawat, D., Chaudhary, D., Kumar, A., Kalwar, A., Mishra, N., & Sharma, D. (2024). Binarized spiking neural network optimized with momentum search algorithm for fetal arrhythmia detection and classification from ECG signals. *Biomedical Signal Processing and Control*, 89, 105713.

- Singh, A.K., & Krishnan, S. (2023). ECG signal feature extraction trends in methods and applications. *BioMedical Engineering OnLine*, 22(1), 22.

- Sinha, V.K., Kar, S.K. (2024). An efficient real-time ECG QRS-complex identification by A-CLT and digital fractional order differentiation. *Biomedical Signal Processing and Control*, 92, 106055.

- Sohal, H., Jain, S. (2019). FPGA implementation of Power-Efficient ECG pre-processing block. International Journal of Recent Technology and Engineering (IJRTE), 8(1), 2899-2904.

- Sohal, H., Jain, S. (2022). FPGA implementation of collateral and sequence pre-processing modules for low power ECG denoising module. *Informatics in Medicine Unlocked*, 28, 100838.

- Swetha, R., Ramakrishnan, S. (2024). Unfolding VLSI Architecture for Mixed Noise Removal and Multiple Classification of ECG Signals. *Circuits, Systems, and Signal Processing*, 43(4), 1993-2015.

- Talukder, S., Singh, R., Bora, S., & Paily, R. (2020). An efficient architecture for QRS detection in FPGA using integer Haar wavelet transform. *Circuits, Systems, and Signal Processing*, 39(7), 3610-3625.

- Talwar, P., Cecil, K. (2023). Adaptive filter and EMD based de-noising method of ECG signals: a review. Am J Multidisc Rese Dev (AJMRD), 5(3), 09-14.

- Thannoon, H.H., Hashim, I.A. (2024). FPGA Implementation of Efficient Adaptive Filter Incorporating Systolic Architecture. Engineering and Technology Journal, 42(2), 261-275.

- Thirrunavukkarasu, R., Santhosh, K., Shivaani, S., Devi, T.M., Srivardhini, R., & Prabhu, S.G. (2021). ECG denoising using Kaiser Bessel Window Filter. In 2021 7th International Conference on Advanced Computing and Communication Systems (ICACCS).

- Vaishnavi, A.S., Greeshma, T., Teja, R.P., Padma, T., & Kumari, C.U. (2023). Noise Removal from ECG Signal using LMS Adaptive Filter Implementation in Xilinx System Generator. In 2023 2nd International Conference on Applied Artificial Intelligence and Computing (ICAAIC).

- Venkatesan, C., Karthigaikumar, P., & Varatharajan, R. (2019). FPGA implementation of modified error normalized LMS adaptive filter for ECG noise removal. *Cluster Computing*, 22 (Suppl 5), 12233-12241.

- Wei, J., Zhang, C., Ma, J., Li, Z., & Liu, M. (2021). An ECG Automatic Detection System with Baseline Drift Removal Based on SG Filter. In 2021 *IEEE 14th International Conference on* ASIC (ASICON).

- Xiao, Q., Lee, K., Mokhtar, S. A., Ismail, I., Pauzi, A.L.b.M., Zhang, Q., & Lim, P.Y. (2023). Deep learning-based ECG arrhythmia classification: A systematic review. *Applied Sciences*, 13(8), 4964.

- Xing, Y., Zhang, L., Hou, Z., Li, X., Shi, Y., Yuan, Y., ... Yan, L. (2022). Accurate ECG classification based on spiking neural network and attentional mechanism for real-time implementation on personal portable devices. *Electronics*, 11(12), 1889.

- Yan, R., Wang, J., Wang, J., Shao, H., & Fang, X. (2023). ECG R-wave detection and its application in left ventricular assist device. *Journal of Circuits, Systems and Computers*, 32(18), 2350308.

- Yang, M., Gao, D., Li, J., Xu, W., & Shi, G. (2024). Superimposed semantic communication for iot-based real-time ecg monitoring. *IEEE Journal of Biomedical and Health Informatics*.

- Zairi, H., Kedir Talha, M., Meddah, K., & Ould Slimane, S. (2020). FPGA-based system for artificial neural network arrhythmia classification. *Neural Computing and Applications*, 32, 4105-4120.

- Zhang, B., Sieler, L., Morère, Y., Bolmont, B., & Bourhis, G. (2017). Dedicated wavelet QRS complex detection for FPGA implementation. In 2017 International Conference on Advanced Technologies for Signal and Image Processing (ATSIP).